Презентация на тему: Способы адресации в микропроцессорных системах

Лекция 6. Способы адресации в микропроцессорных системах

Для взаимодействия с различными модулями в ЭВМ должны быть средства идентификации ячеек внешней памяти, ячеек внутренней памяти, регистров МП и регистров устройств ввода/вывода. Поэтому каждой из запоминающих ячеек присваивается адрес, т.е. однозначная комбинация бит. Количество бит определяет число идентифицируемых ячеек. Обычно ЭВМ имеет различные адресные пространства памяти и регистров МП, а иногда - отдельные адресные пространства регистров устройств ввода/вывода и внутренней памяти. Кроме того, память хранит как данные, так и команды. Поэтому для ЭВМ разработано множество способов обращения к памяти, называемых режимами адресации. Режим адресации памяти - это процедура или схема преобразования адресной информации об операнде в его исполнительный адрес.

Все способы адресации памяти можно разделить на: 1) прямой, когда исполнительный адрес берется непосредственно из команды или вычисляется с использованием значения, указанного в команде, и содержимого какого-либо регистра (прямая адресация, регистровая, базовая, индексная и т.д.); 2) косвенный, который предполагает, что в команде содержится значение косвенного адреса, т.е. адреса ячейки памяти, в которой находится окончательный исполнительный адрес (косвенная адресация). В каждой микроЭВМ реализованы только некоторые режимы адресации, использование которых, как правило, определяется архитектурой МП.

Обработка информации в микропроцессорной системе осуществляется автоматически, путем программного управления. Программа представляет собой алгоритм обработки данных, записанный в виде последовательности команд, которые должны быть выполнены системой для получения требуемого результата. Команда представляет собой код, определяющий операцию обработки информации и данные, участвующие в этой операции. По характеру выполняемых операций все возможные команды условно делят на несколько основных групп: а) команды арифметической обработки; б) команды логической обработки; в) команды передачи (пересылки) кодов; г) команды ввода-вывода; д) команды передачи управления; е) команды управления режимами работы микропроцессора и др.

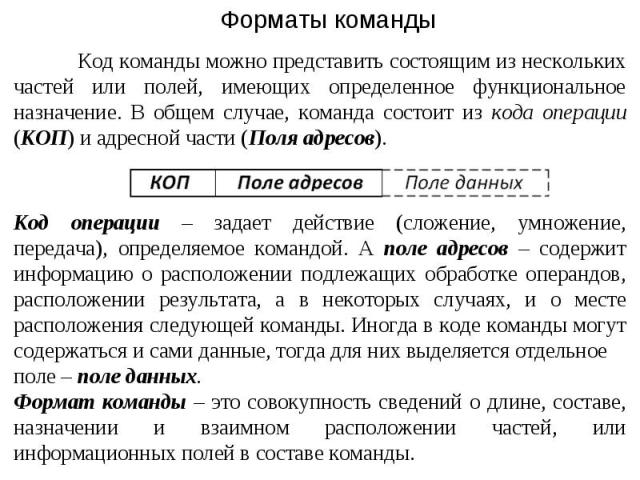

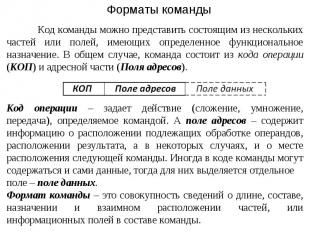

Код команды можно представить состоящим из нескольких частей или полей, имеющих определенное функциональное назначение. В общем случае, команда состоит из кода операции (КОП) и адресной части (Поля адресов).

Двоичный n-разрядный номер ячейки памяти, к которой нужно обратиться в ходе выполнения вычислительного процесса, принадлежащий этой и только этой ячейке – называется полным физическим или исполнительным адресом. Процедура вычисления исполнительного адреса определяется способами адресации и расположением самих операндов, которые могут находиться: - в самой команде; - в регистрах микропроцессора; - в памяти, т.е. в ОЗУ; - в устройствах ввода-вывода.

Следует различать понятия исполнительный адрес и адресный код в формате команды. Исполнительный адрес — это номер ячейки памяти, к которой производится фактическое обращение. Адресный код — это информация об адресе операнда, содержащаяся в команде. В современных микросистемах, адресный код часто не совпадает с исполнительным адресом. Выбор способов адресации, формирования исполнительного адреса и преобразования адресов является одним из важнейших вопросов разработки ЭВМ.

Команды разных микропроцессорных систем могут использовать различные способы адресации, которые применяются как сами по себе, так и совместно друг с другом. Рассмотрим некоторые способы адресации, широко используемые в современных ЭВМ: Неявная адресация. В команде не содержится явных указаний об адресе участвующего в операции операнда или адреса, по которому помещается результат операции, но этот адрес, так или иначе, подразумевается. И в конечном итоге жестко привязан к выполняемой операции. Прямая адресация. Исполнительный адрес совпадает с адресной частью команды. Этот способ адресации был общепринятым в первых вычислительных машинах и продолжает применяться в настоящее время в комбинации с другими способами.

Непосредственная адресация. В команде содержится не адрес операнда, а непосредственно сам операнд. Такая адресация удобна для хранения различного рода констант. Относительная адресация или базирование. Исполнительный адрес определяется суммой адресного кода команды АК и некоторого числа АБ называемого базовым адресом: АИ = АБ + АК Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти. Для этого число разрядов в базовом адресе выбирают таким, чтобы можно было адресовать любую ячейку ОЗУ, а адресный код АК самой команды используют для представления лишь сравнительно короткого «смещения».

Регистровая адресация. Для уменьшения длины адресного кода, используются регистры микропроцессора, в качестве фиксированных ячеек с короткими адресами. (Если таких регистров 16, то для адресации одного из них достаточно четырех двоичных разрядов.). Применение регистровой адресации наряду с сокращением длины адресов операндов, позволяет увеличить скорость выполнения операций, так как уменьшается число обращений к ОЗУ через системную магистраль. Косвенная адресация. Адресный код команды указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Таким образом, косвенная адресация

Автоинкрементная и автодекрементная адресации. Обеспечивает эффективную работу с массивами данных, за счет формирования адреса следующего элемента массива путем автоматического приращения или уменьшения адреса текущего обрабатываемого элемента массива, при его косвенной адресации

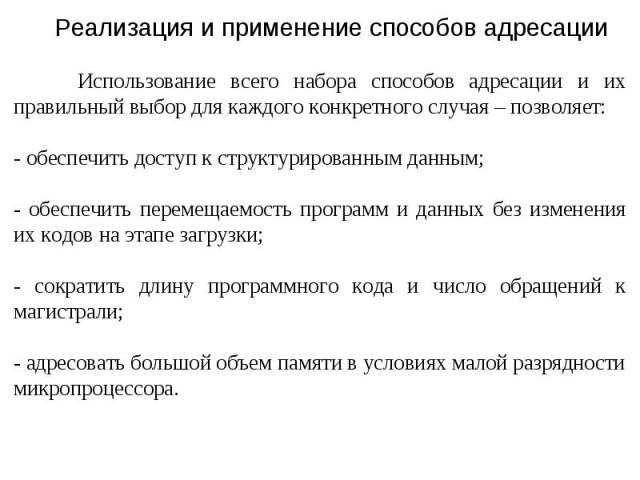

Использование всего набора способов адресации и их правильный выбор для каждого конкретного случая – позволяет: - обеспечить доступ к структурированным данным; - обеспечить перемещаемость программ и данных без изменения их кодов на этапе загрузки; - сократить длину программного кода и число обращений к магистрали; - адресовать большой объем памяти в условиях малой разрядности микропроцессора.