Презентация на тему: Микропроцессоры и микроконтроллеры. Часть 3

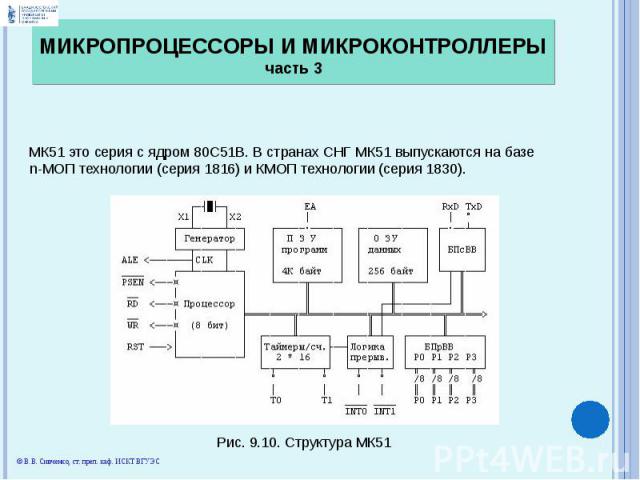

МК51 это серия с ядром 80С51В. В странах СНГ МК51 выпускаются на базе n-МОП технологии (серия 1816) и КМОП технологии (серия 1830). МК51 это серия с ядром 80С51В. В странах СНГ МК51 выпускаются на базе n-МОП технологии (серия 1816) и КМОП технологии (серия 1830).

В МК51 используются следующие сигналы: В МК51 используются следующие сигналы: ALE - строб адреса; PSEN\ - строб чтения внешней памяти программ; RD\,WR\- стробы чтения и записи внешней памяти данных; EA\ - разрешение обращения во внутреннюю память программ; T0,T1 - входы счетчиков внешних событий; INT0,INT1- запросы внешних радиальных прерываний; RxD - вход данных последовательного канала; TxD - выход данных последовательного канала. В состав МК51 входят параллельные 8-разрядные квазидвунаправленные порты P0..P3. Порт Р3 может быть использован для ввода и вывода управляющих сигналов. Таким образом, в циклах обращения к внешним ресурсам на линиях порта P3 работают управляющие сигналы, а при отсутствии необходимости управления внешними ресурсами эти же линии могут быть использованы как линии порта.

МК51 позволяет управлять пятью (частично пересекающимися) адресными пространствами памяти, четыре из которых являются областями данных: МК51 позволяет управлять пятью (частично пересекающимися) адресными пространствами памяти, четыре из которых являются областями данных: RSEG - пространство регистров (4*8 байт); DSEG - пространство внутренней памяти данных (256 байт); BSEG - битовое пространство данных (256 бит); XSEG - пространство внешней памяти данных (до 64К байт); CSEG - пространство программного кода (до 64К байт). Пространства RSEG и BSEG частично пересекаются, физически совмещаются с DSEG и образуют единую внутреннюю среду для хранения данных. Это позволяет одни и те же данные рассматривать с разных позиций (ячейка памяти, регистр, битовое поле, порт ввода/вывода и т.п.) и организовывать наиболее удобный для данного случая доступ к ним. Характерно, что все порты ввода/вывода, системные регистры, таймеры так же отображены на пространство DSEG.

Пространство регистров представлено четырьмя банками регистров по 8 в каждом, а так же 16-разрядными программным счетчиком PC и регистром косвенного адреса DPTR, 8-разрядными аккумуляторами A и B, указателем стека SP и регистром PSW. Пространство регистров представлено четырьмя банками регистров по 8 в каждом, а так же 16-разрядными программным счетчиком PC и регистром косвенного адреса DPTR, 8-разрядными аккумуляторами A и B, указателем стека SP и регистром PSW. Все регистры, кроме PC, отображаются на DSEG. PSW[7] - CY - перенос из старшего (7) разряда АЛБ; PSW[6] - AC - перенос из третьего разряда АЛБ; PSW[5] - F0 - флаг пользователя. Кроме того, формат PSW включает двухбитовое поле PSW[4:3] - RS номера банка регистров и флаги арифметического переполнения OV (PSW[2]) и четности P (PSW[0]). Флаги CY, AC и OV отражают признаки результата последней арифметической операции, а P - четность содержимого аккумулятора A. Расширение аккумулятора B используется в командах умножения и деления, а в остальных операциях - как обычная ячейка памяти. Программный счетчик адресует пространство памяти программ CSEG объемом до 64K байт, причем переход из области внутренней памяти программ к внешней осуществляется автоматически.

Указатель данных DPTR используется для обращения к XSEG и при пересылке констант из CSEG в A. Кроме того, содержимое DPTR используется а качестве смещения в команде перехода. Указатель стека SP образует системный стек глубиной до 256 байт. SP хранит адрес последнего занесенного байта и растет при записи в сторону больших адресов. Указатель данных DPTR используется для обращения к XSEG и при пересылке констант из CSEG в A. Кроме того, содержимое DPTR используется а качестве смещения в команде перехода. Указатель стека SP образует системный стек глубиной до 256 байт. SP хранит адрес последнего занесенного байта и растет при записи в сторону больших адресов. Регистры R0, R1 каждого банка используются в качестве указателей данных. При сбросе машины в A, B, PC и DPTR загружаюся 0h, а в SP - 07h.

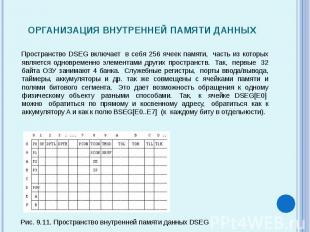

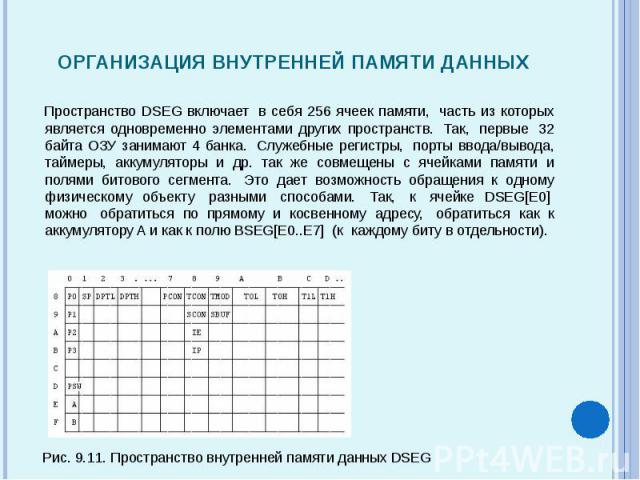

Пространство DSEG включает в себя 256 ячеек памяти, часть из которых является одновременно элементами других пространств. Так, первые 32 байта ОЗУ занимают 4 банка. Служебные регистры, порты ввода/вывода, таймеры, аккумуляторы и др. так же совмещены с ячейками памяти и полями битового сегмента. Это дает возможность обращения к одному физическому объекту разными способами. Так, к ячейке DSEG[E0] можно обратиться по прямому и косвенному адресу, обратиться как к аккумулятору A и как к полю BSEG[E0..E7] (к каждому биту в отдельности). Пространство DSEG включает в себя 256 ячеек памяти, часть из которых является одновременно элементами других пространств. Так, первые 32 байта ОЗУ занимают 4 банка. Служебные регистры, порты ввода/вывода, таймеры, аккумуляторы и др. так же совмещены с ячейками памяти и полями битового сегмента. Это дает возможность обращения к одному физическому объекту разными способами. Так, к ячейке DSEG[E0] можно обратиться по прямому и косвенному адресу, обратиться как к аккумулятору A и как к полю BSEG[E0..E7] (к каждому биту в отдельности).

![Память программ адресуется PC[15:0] и может составлять до 64К байт, причем Память программ адресуется PC[15:0] и может составлять до 64К байт, причем](https://fs1.ppt4web.ru/images/95284/138350/310/img6.jpg)

Память программ адресуется PC[15:0] и может составлять до 64К байт, причем младшие 4 К могут располагаться непосредственно на кристалле, а остальная память внешнее ЗУ. С точки зрения программиста внешняя и внутренняя память программ представляют единое адресное пространство. Память программ адресуется PC[15:0] и может составлять до 64К байт, причем младшие 4 К могут располагаться непосредственно на кристалле, а остальная память внешнее ЗУ. С точки зрения программиста внешняя и внутренняя память программ представляют единое адресное пространство. Имеются «особые точки» CSEG: RESET 0000h - стартовый адрес; EXTI0 0003h - внешнее прерывание 0; TIMER0 000Bh - прерывание от таймера/счетчика T0; EXTI1 0013h - внешнее прерывание 1; TIMER1 001Bh - прерывание от таймера/счетчика T1; SINT 0023h - прерывание последовательного порта;

Питание МК51 осуществляется от одного источника +5В. Кварцевый резонатор 3,5..12 МГц подключается к выводам Х1, Х2; возможно подключение внешнего тактового генератора через Х1. Питание МК51 осуществляется от одного источника +5В. Кварцевый резонатор 3,5..12 МГц подключается к выводам Х1, Х2; возможно подключение внешнего тактового генератора через Х1. OSC/2 - основная внутренняя тактовая частота CLK. Первая половина периода CLK фаза P1, вторая - P2. Каждый машинный цикл состоит из шести периодов CLK: состояний S1, S2, .. S6 или двенадцати периодов OSC, называемых фазами S1P1, S1P2, S2P1, .. S6P, S6P2. Каждый машинный цикл сопровождается генерацией двух стробов ALE длительностью в один период CLK - S1P2..S2P1, S4P2.. S5P1. Командный цикл (КЦ) содержит один или несколько машинных циклов (МЦ) и отсчитывается от S1P1. По фазе S1P2 в IR фиксируется код операции, второй байт двухбайтовой команды читается в S4P2 того же МЦ, третий байт трехбайтовой - в S1P2 следующего МЦ. Таким образом, для ввода каждого байта команды требуется один полуцикл. Во время всех оставшихся полуциклов в фазах S1P2 и S4P2 читается код операции следующей размещенной в памяти команды, однако он не помещается в IR и не инкрементируется PC. Текущий КЦ всегда завершается в S6P2. Вслед за этим начинается S1, в котором в IR вводится новый байт.

Обращение к внешней памяти данных XSEG по команде MOVX требует второго МЦ, в котором не вырабатывается первый строб ALE. На рис. 3.7 приведена временная диаграмма обращения к XSEG. Для приведение МК51 в исходное состояние необходимо подать на вход RST импульс H-уровня длительностью не менее 24 периодов OSC (два МЦ) при условии что генератор запущен. Обращение к внешней памяти данных XSEG по команде MOVX требует второго МЦ, в котором не вырабатывается первый строб ALE. На рис. 3.7 приведена временная диаграмма обращения к XSEG. Для приведение МК51 в исходное состояние необходимо подать на вход RST импульс H-уровня длительностью не менее 24 периодов OSC (два МЦ) при условии что генератор запущен.

К "внешним" устройствам МК51 отнесем: К "внешним" устройствам МК51 отнесем: 4 параллельных двунаправленных порта ввода/вывода P0..P3; буфер SBUF и регистр управления SCON последовательного канала; таймеры/счетчики T0, T1, их регистр управления TCON и регистр режимов TMOD; регистры управления подсистемой прерываний: регистр приоритетов IP и регистр маски IE; регистр управления машиной PCON. В состав МК51 входит дуплексный последовательный канал связи с буферизацией, который может быть запрограммирован для работы в одном из четырех режимов: режим "0" - синхронный ввод/вывод с частотой OSC/12; режим "1" - асинхронный с 8-бит. кадром, частота k*f; режим "2" - асинхронный с 9-бит. кадром, частота k*OSC/32; режим "3" - асинхронный с 9-бит. кадром, частота k*f; где k {1, 1/2}, f - частота переполнения T1 (FOV), деленная на 16.

Архитектура МК51 поддерживает двухуровневую радиальную приоритетную подсистему прерываний (ПП) с шестью источниками запросов. Для приема внешних прерываний служат входы INT0\, INT1\. Архитектура МК51 поддерживает двухуровневую радиальную приоритетную подсистему прерываний (ПП) с шестью источниками запросов. Для приема внешних прерываний служат входы INT0\, INT1\. Источниками внутренних запросов могут служить сигналы переполнения таймеров T0, T1 и сигнал окончания работы последовательного канала

Система команд включает 111 команд - однобайтовых (49), двухбайтовых (45) и трехбайтовых (17). Все команды выполняются за 1 или 2 МЦ (16 тактов CLK в каждом), за исключением команд умножения и деления MUL и DIV, для выполнения которых требуется 4 МЦ. Большинство двухбайтовых команд - одноцикловые, а все трехбайтовые -двухцикловые. За один МЦ в МК51 можно вводить до двух байтов программного кода. Система команд включает 111 команд - однобайтовых (49), двухбайтовых (45) и трехбайтовых (17). Все команды выполняются за 1 или 2 МЦ (16 тактов CLK в каждом), за исключением команд умножения и деления MUL и DIV, для выполнения которых требуется 4 МЦ. Большинство двухбайтовых команд - одноцикловые, а все трехбайтовые -двухцикловые. За один МЦ в МК51 можно вводить до двух байтов программного кода. МК51 работает с данными четырех основных типов - битами, полубайтами (4 бита), байтами и адресами (16 бит). Наиболее часто используемой единицей данных является байт: внутренние магистрали данных имеют 8-битный размер. Программная память, внутренняя память и внешняя память данных запоминают и возвращают данные в виде байтов. Кроме этого, имеется много команд, которые работают с одиночными битами. Бит может быть установлен, очищен, проинвертирован, логически скомбинирован с флагом переноса и проверен для выполнения последующих переходов. Полубайт (двоично-десятичная упакованная цифра) обычно мало применяется в МК51, но двоично-десятичная арифметика может выполняться без преобразования операндов в двоичное представление.

Команды, которые используют 16-битные адреса, имеют дело с указателем данных (16-битный регистр DPTR ) и с программным счетчиком (переходы и вызовы подпрограммы). Использование команд сложения с битом переноса (ADDC) и вычитание с заемом (SUBB) делает программирование 16-битной арифметики относительно простым. Программно-доступными объектами в составе ОМЭВМ являются: аппаратные регистры, четыре банка по восемь регистров R0..R7,R0..R7 и 128 ячеек внутренней памяти данных - с адресами 00H..7FH. Кроме того, по специальным командам MOVX и MOVC может быть доступна внешняя память данных и программ. В МК51 возможна битовая адресация аппаратных регистров и части внутренней памяти. При программировании следует иметь в виду, что в качестве регистров R0..R7 банка 0 используются ячейки внутренней памяти данных с адресами 00H..07H, банка 1 - 08Н..0FН, банка 2 - 10Н..17Н, банка 3 - 18Н..1FH. Команды, которые используют 16-битные адреса, имеют дело с указателем данных (16-битный регистр DPTR ) и с программным счетчиком (переходы и вызовы подпрограммы). Использование команд сложения с битом переноса (ADDC) и вычитание с заемом (SUBB) делает программирование 16-битной арифметики относительно простым. Программно-доступными объектами в составе ОМЭВМ являются: аппаратные регистры, четыре банка по восемь регистров R0..R7,R0..R7 и 128 ячеек внутренней памяти данных - с адресами 00H..7FH. Кроме того, по специальным командам MOVX и MOVC может быть доступна внешняя память данных и программ. В МК51 возможна битовая адресация аппаратных регистров и части внутренней памяти. При программировании следует иметь в виду, что в качестве регистров R0..R7 банка 0 используются ячейки внутренней памяти данных с адресами 00H..07H, банка 1 - 08Н..0FН, банка 2 - 10Н..17Н, банка 3 - 18Н..1FH. В системе команд МК51 используются регистровая, прямая, косвенная и непосредственная адресация. При регистровой адресации операнды находятся в регистрах, имена которых определяются кодом операции команды. Эта адресация используется для обращения к регистрам выбранного банка рабочих регистров, к регистрам А, В, DPTR и к флагу переноса С.

По прямому адресу можно обращаться к аппаратным регистрам и внутренней памяти. Используется также прямая битовая адресация. Косвенно можно адресоваться к ячейкам внутренней и внешней памяти данных через регистры R0,R1 текущего банка. По прямому адресу можно обращаться к аппаратным регистрам и внутренней памяти. Используется также прямая битовая адресация. Косвенно можно адресоваться к ячейкам внутренней и внешней памяти данных через регистры R0,R1 текущего банка. К любой ячейке внешней памяти (данных и программ) можно обратиться с использованием регистра DPTR. По типу операций можно выделить следующие классы команд: пересылки; арифметические и логические; передачи управления; специальные команды.

Это особо малый микроконтроллер. Простейший микроконтроллер имеет 8 выводов. Микроконтроллер 8-ми разрядный с Гарвардской архитектурой, что повышает производительность. Одновременно считывается команда и происходит обращение за данными. В некоторых микроконтроллерах есть операции умножения, деления, операции с плавающей точкой. Система команд компактная – не более 51 команды (LOW, LITLE и HIGH – 51 команда). Есть банки регистров как МК51. Это особо малый микроконтроллер. Простейший микроконтроллер имеет 8 выводов. Микроконтроллер 8-ми разрядный с Гарвардской архитектурой, что повышает производительность. Одновременно считывается команда и происходит обращение за данными. В некоторых микроконтроллерах есть операции умножения, деления, операции с плавающей точкой. Система команд компактная – не более 51 команды (LOW, LITLE и HIGH – 51 команда). Есть банки регистров как МК51. Есть ПЗУ разных типов и перифирийные устройства (АЦП, ЦАП). В составе перифирийных устройств имеется несколько выводов последовательного интерфейса – обычный RS232, интерфейс I2C фирмы Philips, SPI. Контроллеры PIC могут быть использованы как ?умные? перифирийные устройства, т.е. SLAVE – контроллер может быть подсоединен к управляющему контроллеру PIC как обычное перифирийное устройство через порт (или линю данных). Очень развиты перифирийные средства коммуникации (I2C, SPI, RS232, порты). На основе PIC может быть организованна сеть микроконтроллеров (через шину I2C). У SPI и I2C общая особенность: для передачи используется два провода. Интерфейс SPI работает со стробиованием по фронту сигнала (клока), т.е. по одной линии передаются данные, по другой – клок. В I2C стробирование осуществляется по уровню. В обоих интерфейсах Master обеспечивает выдачу сигналов тактирования.

![Память программ адресуется PC[15:0] и может составлять до 64К байт, причем младшие 4 К могут располагаться непосредственно на кристалле, а остальная память внешнее ЗУ. С точки зрения программиста внешняя и внутренняя память п… Память программ адресуется PC[15:0] и может составлять до 64К байт, причем младшие 4 К могут располагаться непосредственно на кристалле, а остальная память внешнее ЗУ. С точки зрения программиста внешняя и внутренняя память п…](https://fs1.ppt4web.ru/images/95284/138350/640/img6.jpg)